- 您现在的位置:买卖IC网 > Sheet目录3890 > PIC16C717T-E/SS (Microchip Technology)IC MCU OTP 2KX14 A/D PWM 20SSOP

2002 Microchip Technology Inc.

DS41120B-page 121

PIC16C717/770/771

12.3

RESET

The PIC16C717/770/771 devices have several differ-

ent RESETS. These RESETS are grouped into two

classifications; power-up and non-power-up. The

power-up type RESETS are the Power-on and Brown-

out Resets which assume the device VDD was below its

normal operating range for the device’s configuration.

The non power-up type RESETS assume normal oper-

ating limits were maintained before/during and after the

RESET.

Power-on Reset (POR)

Programmable Brown-out Reset (PBOR)

MCLR Reset during normal operation

MCLR Reset during SLEEP

WDT Reset (during normal operation)

Some registers are not affected in any RESET condi-

tion. Their status is unknown on a Power-up Reset and

unchanged in any other RESET. Most other registers

are placed into an initialized state upon RESET, how-

ever they are not affected by a WDT Reset during

SLEEP, because this is considered a WDT Wake-up,

which is viewed as the resumption of normal operation.

Several status bits have been provided to indicate

which

RESET

occurred

(see

See

Table 12-6 for a full description of RESET states of all

registers.

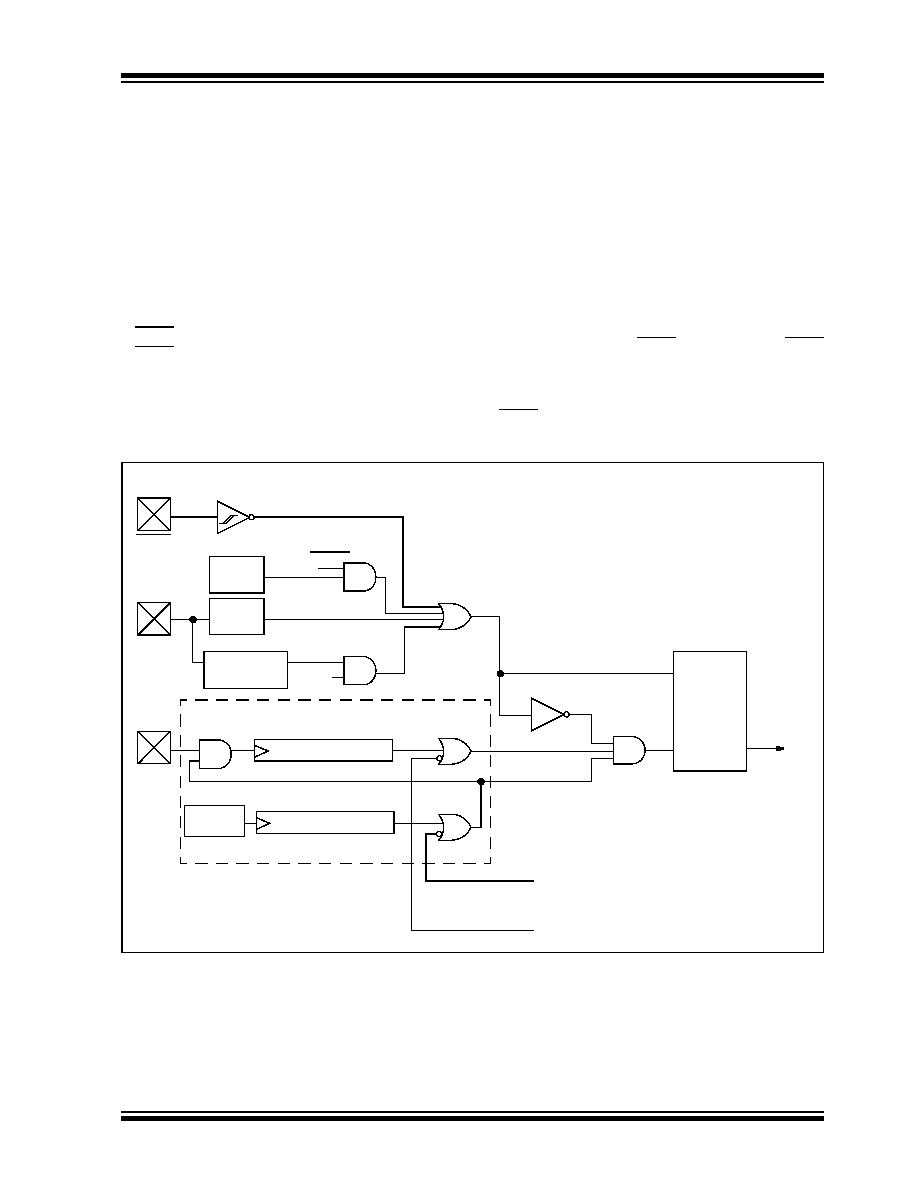

A simplified block diagram of the On-Chip Reset circuit

is shown in Figure 12-4.

These devices have a MCLR noise filter in the MCLR

Reset path. The filter will detect and ignore small

pulses.

It should be noted that a WDT Reset does not drive

MCLR pin low.

FIGURE 12-4:

SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

S

R

Q

External

RESET

MCLR

VDD

OSC1

WDT

Module

VDD rise

detect

OST/PWRT

Dedicated

Oscillator

Power-on Reset

OST

10-bit Ripple counter

PWRT

Chip_Reset

10-bit Ripple counter

Enable OST

Enable PWRT

SLEEP

Brown-out

Programmable

BODEN

Time-out

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC16LC770T-E/SO

IC MCU OTP 2KX14 A/D PWM 20SOIC

PIC16C771T/SO

IC MCU OTP 4KX14 A/D PWM 20SOIC

PIC16LC717T-I/SS

IC MCU OTP 2KX14 A/D PWM 20SSOP

PIC16C717T/SS

IC MCU OTP 2KX14 A/D PWM 20SSOP

PIC16LC770T-I/SO

IC MCU OTP 2KX14 A/D PWM 20SOIC

PIC16LC771T-E/SS

IC MCU OTP 4KX14 A/D PWM 20SSOP

PIC16C771T-E/SS

IC MCU OTP 4KX14 A/D PWM 20SSOP

PIC16LC771T-I/SO

IC MCU OTP 4KX14 A/D PWM 20SOIC

相关代理商/技术参数

PIC16C717T-I/SO

功能描述:8位微控制器 -MCU 3.5KB 256 RAM 16 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16C717T-I/SS

功能描述:8位微控制器 -MCU 3.5KB 256 RAM 16 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16C71T-04/SO

功能描述:8位微控制器 -MCU 1.75KB 36 RAM 13 I/O 4MHz SOIC18 RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16C71T-04I/SO

功能描述:8位微控制器 -MCU 1.75KB 36 RAM 13 I/O 4MHz Ind Temp SOIC18 RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16C71T-20/SO

功能描述:8位微控制器 -MCU 1.75KB 36 RAM 13 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16C71T-20I/SO

功能描述:8位微控制器 -MCU 1.75KB 36 RAM 13 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16C72/JW

功能描述:8位微控制器 -MCU 3.5KB 128 RAM 22 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16C72-04/SO

功能描述:8位微控制器 -MCU 3.5KB 128 RAM 22 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT